I.MX6ULL 时钟配置

时钟来源和生成

包括以下三个时钟来源:

- 外部晶振,高速晶振频率24Mhz,低速晶振频率32.768KHz

- 低压差分信号 (LVDS) I/O 端口,用于从外部获取时钟信号

- 锁相环(PLL),主时钟包含七个 PLL。其中两个 PLL 分别配备四个相位小数分频器 (PFD),以生成额外的频率。

七个PLL包括:

- PLL1(ARM_PLL),ARM内核时钟,最高可倍频至1.3GHz(但MCU最高仅支持到1.0GHz)

- PLL2(SYS_PLL/528_PLL),固定倍频22倍,从外部高速晶振的24MHz倍频产生528MHz,自带四个PFD。通常528_PLL和4路PFD是MX6U内部系统总线的时钟源,如逻辑单元、DDR、NAND/NOR设备等

- PLL3(USB1_PLL),USB PHY的第一个实例(USBPHY1,也称为 OTG PHY)一起使用。此 PLL 驱动四个 PFD(PLL3_PFD0…PLL3_PFD3)并以固定乘数 20 运行。这导致 VCO 频率为 480 MHz,振荡器为 24 MHz。主 PLL 输出及其 PFD 输出用作许多需要恒定频率的时钟根的输入,例如 UART 和其他串行接口、音频接口等

- PLL4(Audio_PLL),用于生成具有标准音频频率的低抖动和高精度音频时钟。其频率范围为 650 MHz 至 1300 MHz,频率分辨率优于 1 Hz。该时钟主要用作串行音频接口的时钟和外部音频编解码器的参考时钟。

- PLL5(Video_PLL),用于生成具有标准视频频率的低抖动和高精度视频时钟。PLL 振荡器频率范围为 650 MHz 至 1300 MHz,频率分辨率优于 1 Hz。该时钟主要用作显示和视频接口的时钟。

- PLL6(ENET_PLL),固定(20+5/6)倍频,输出500MHz,用于生成以太网

- PLL7(USB2_PLL),专门为 USB2 PHY(USBPHY2,也称为 OTG PHY)提供时钟,固定倍频 20,输出频率480MHz

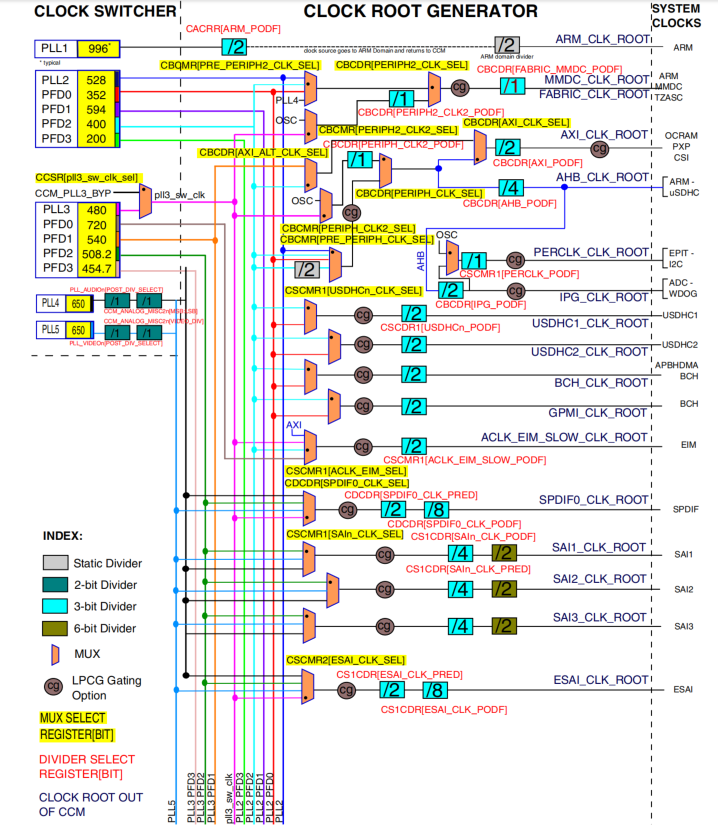

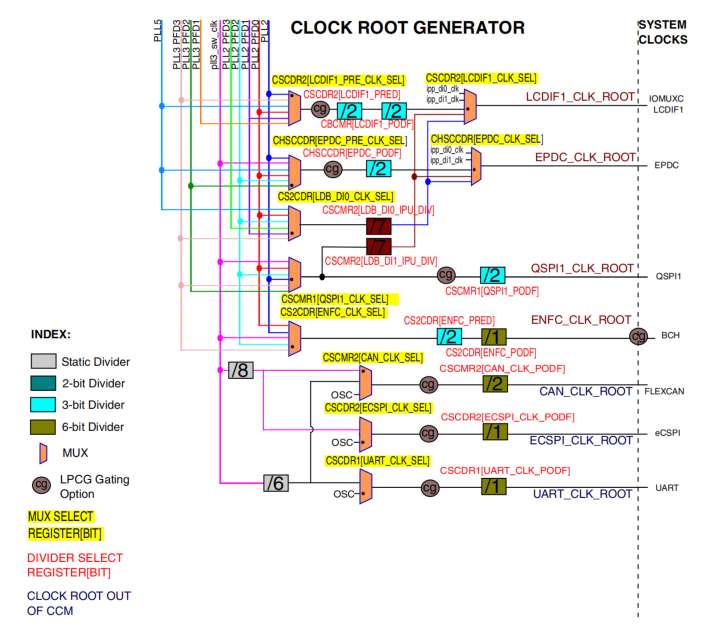

CCM时钟树

具体参见手册第629页。

时钟配置

以ARM时钟配置为例:

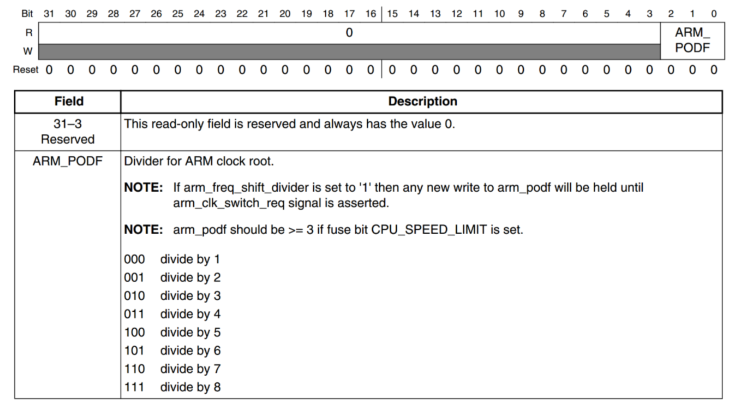

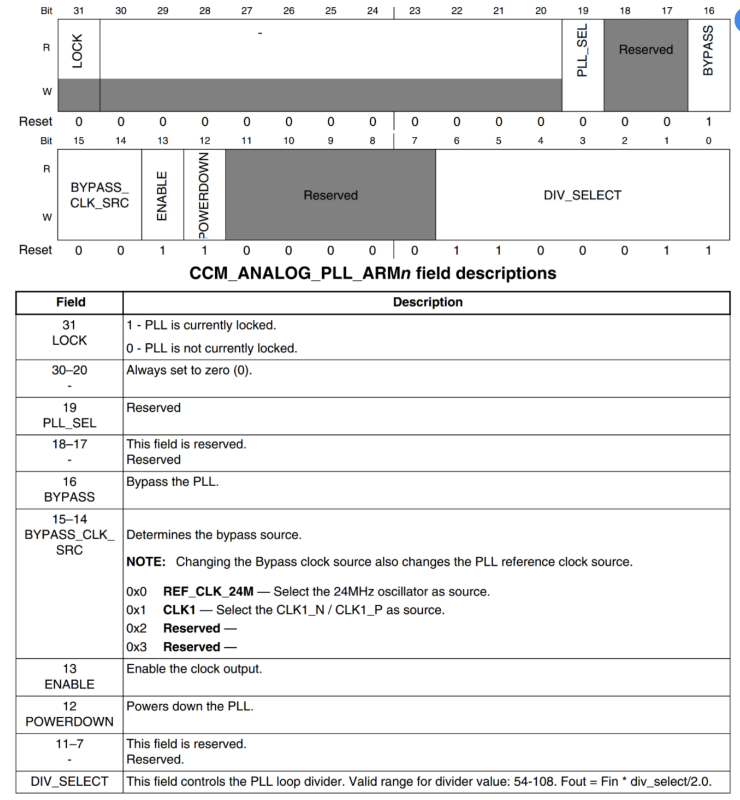

时钟从PLL1的996MHz开始,通过寄存器CCM_CACRR的ARM_PODF位进行分频,可选1/2/4/8分频,然后得到ARM时钟ARM_CLK_ROOT。灰色的/2分频并未实际效果。其中PLL1频率可通过寄存器CCM_ANALOG_PLL_ARMn设置。

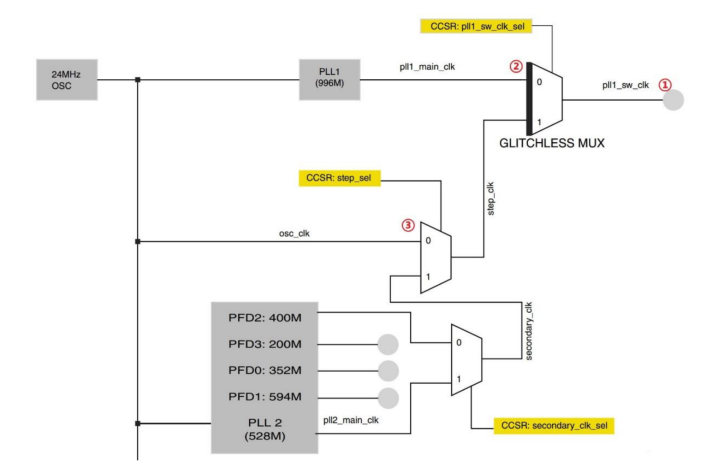

修改PLL1时钟时要首先要切换内核时钟源。

- PLL1最终输出时钟频率。

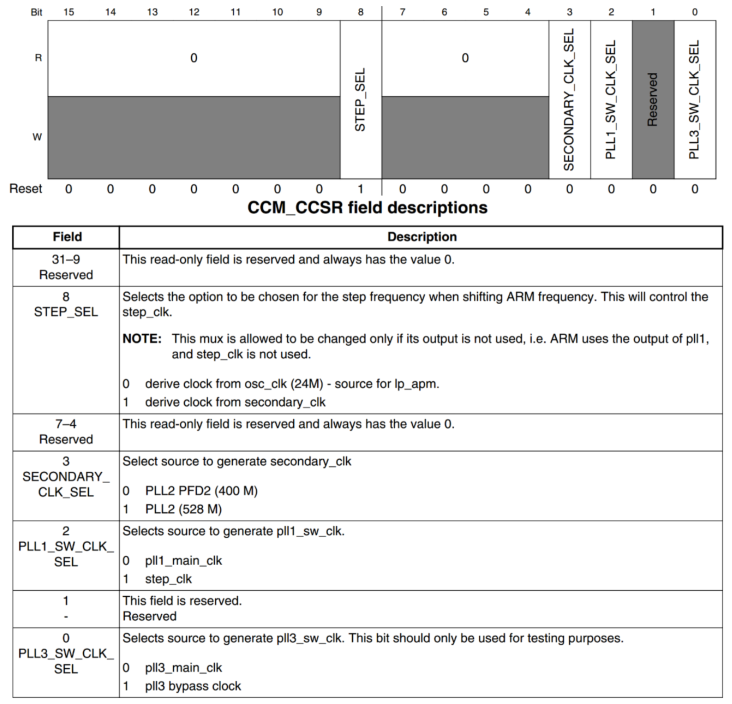

- 选择器,用于选择pll1的时钟源,由CCM_CCSR的PLL1_SW_CLK_SEL位决定。默认为pll1_main_clk,但如果要调整pll1_main_clk频率,则首先应将pll_sw_clk切换至step_clk,调整完成后再切换回来。

- 选择器,用于选择step_clk的时钟源,由CCM_CCSR的STEP_SEL位决定。默认为osc_clk,即外部高速晶振。

至此,修改I.MX6U主频的步骤可以归纳为:

- 设置CCM_CCSR的STEP_SEL位,设置step_clk时钟源为外部24MHz高速晶振

- 设置CCM_CCSR的PLL1_SW_CLK_SEL位,设置pll_sw_clk来源为step_clk=24Mhz

- 设置CCM_ANALOG_PLL_ARMn,将pll1_main_clk设置为1056MHz

- 设置CCM_CCSR的PLL1_SW_CLK_SEL位,将pll1_sw_clk时钟源切换回pll1_main_clk

- 设置CCM_CACRR的ARM_PODF为2分频,完成分频设置

其他的时钟配置方式大同小异。

代码

1 | |

I.MX6ULL 时钟配置

http://akichen891.github.io/2025/03/03/时钟配置/